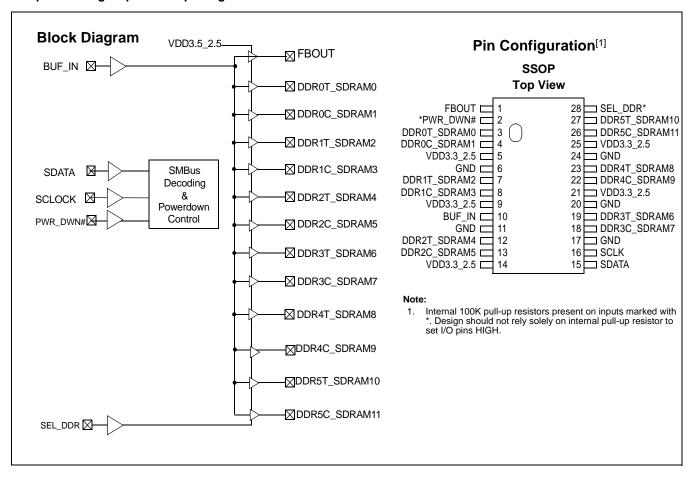

# 12 Output Buffer for 2 DDR and 3 SDRAM DIMMS

#### **Features**

- · One input to 12 output buffer/drivers

- Supports up to 2 DDR DIMMs or 3 SDRAM DIMMS

- One additional output for feedback

- · SMBus interface for individual output control

- Low skew outputs (< 100 ps)

- Supports 266 MHz and 333 MHz DDR SDRAM

- Dedicated pin for power management support

- Space-saving 28-pin SSOP package

#### **Functional Description**

The W256 is a 3.3V/2.5V buffer designed to distribute high-speed clocks in PC applications. The part has 12 outputs. Designers can configure these outputs to support 3 unbuffered standard SDRAM DIMMs and 2 DDR DIMMs. The W256 can be used in conjunction with the W250-02 or similar clock synthesizer for the VIA Pro 266 chipset.

The W256 also includes an SMBus interface which can enable or disable each output clock. On power-up, all output clocks are enabled (internal pull-up).

# **Pin Summary**

| Name                               | Pins                 | Description                                                                                                                                                                                                    |

|------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEL_DDR                            | 28                   | Input to configure for DDR-ONLY mode or STANDARD SDRAM mode.  1 = DDR-ONLY mode.  0 = STANDARD SDRAM mode.  When SEL_DDR is pulled HIGH or configured for DDR-ONLY mode, all                                   |

|                                    |                      | the buffers will be configured as DDR outputs.                                                                                                                                                                 |

|                                    |                      | Connect VDD3.3_2.5 to a 2.5V power supply in DDR-ONLY mode.                                                                                                                                                    |

|                                    |                      | When SEL_DDR is pulled LOW or configured for STANDARD SDRAM output, all the buffers will be configured as STANDARD SDRAM outputs.                                                                              |

|                                    |                      | Connect VDD3.3_2.5 to a 3.3V power supply in STANDARD SDRAM mode.                                                                                                                                              |

| SCLK                               | 16                   | SMBus clock input                                                                                                                                                                                              |

| SDATA                              | 15                   | SMBus data input                                                                                                                                                                                               |

| BUF_IN                             | 10                   | Reference input from chipset. 2.5V input for DDR-ONLY mode; 3.3V input for STANDARD SDRAM mode.                                                                                                                |

| FBOUT                              | 1                    | Feedback clock for chipset. Output voltage depends on VDD3.3_2.5V.                                                                                                                                             |

| PWR_DWN#                           | 2                    | Active LOW input to enable Power Down mode; all outputs will be pulled LOW.                                                                                                                                    |

| DDR[0:5]T_SDRAM<br>[0,2,4,6,8,10]  | 3, 7, 12, 19, 23, 27 | Clock outputs. These outputs provide copies of BUF_IN. Voltage swing depends on VDD3.3_2.5 power supply.                                                                                                       |

| DDR[0:5]C_SDRAM<br>[1,3,5,7,9, 11] | 4, 8, 13, 18, 22, 26 | Clock outputs. These outputs provide complementary copies of BUF_IN when SEL_DDR is active. These outputs provide copies of BUF_IN when SEL_DDR is inactive. Voltage swing depends on VDD3.3_2.5 power supply. |

| VDD3.3_2.5                         | 5, 9, 14, 21, 25     | Connect to 2.5V power supply when W256 is configured for DDR-ONLY mode. Connect to 3.3V power supply, when W256 is configured for standard SDRAM mode.                                                         |

| GND                                | 6, 11, 17, 20, 24    | Ground                                                                                                                                                                                                         |

### **Serial Configuration Map**

The Serial bits will be read by the clock driver in the following order:

Byte 0 - Bits 7, 6, 5, 4, 3, 2, 1, 0 Byte 1 - Bits 7, 6, 5, 4, 3, 2, 1, 0 .

Byte N - Bits 7, 6, 5, 4, 3, 2, 1, 0

- Reserved and unused bits should be programmed to "0".

- SMBus Address for the W256 is:

| A6 | A5 | A4 | А3 | A2 | <b>A</b> 1 | A0 | R/W |

|----|----|----|----|----|------------|----|-----|

| 1  | 1  | 0  | 1  | 0  | 0          | 1  |     |

# Byte 6: Outputs Active/Inactive Register (1 = Active, 0 = Inactive), Default = Active

| Bit   | Pin#   | Description                     | Default |

|-------|--------|---------------------------------|---------|

| Bit 7 |        | Reserved, drive to 0            | 0       |

| Bit 6 |        | Reserved, drive to 0            | 0       |

| Bit 5 |        | Reserved, drive to 0            | 0       |

| Bit 4 | 1      | FBOUT                           | 1       |

| Bit 3 | 27, 26 | DDR5T_SDRAM10,<br>DDR5C_SDRAM11 | 1       |

| Bit 2 |        | Reserved, drive to 0            | 1       |

| Bit 1 | 23, 22 | DDR4T_SDRAM8,<br>DDR4C_SDRAM9   | 1       |

| Bit 0 |        | Reserved, drive to 0            | 1       |

# Byte 7: Outputs Active/Inactive Register (1 = Active, 0 = Inactive), Default = Active

| Bit   | Pin#   | Description                   | Default |

|-------|--------|-------------------------------|---------|

| Bit 7 |        | Reserved, drive to 0          | 1       |

| Bit 6 | 19, 18 | DDR3T_SDRAM6,<br>DDR3C_SDRAM7 | 1       |

| Bit 5 | 12, 13 | DDR2T_SDRAM4,<br>DDR2C_SDRAM5 | 1       |

| Bit 4 |        | Reserved, drive to 0          | 1       |

| Bit 3 |        | Reserved, drive to 0          | 1       |

| Bit 2 | 7, 8   | DDR1T_SDRAM2,<br>DDR1C_SDRAM3 | 1       |

| Bit 1 |        | Reserved, drive to 0          | 1       |

| Bit 0 | 3, 4   | DDR0T_SDRAM0,<br>DDR0C_SDRAM1 | 1       |

# **PRELIMINARY**

W256

# **Maximum Ratings**

Supply Voltage to Ground Potential ......-0.5 to +7.0V DC Input Voltage (except BUF\_IN) ......-0.5V to  $V_{DD}$ +0.5

| Storage Temperature            | _65°C to +150°C |

|--------------------------------|-----------------|

| Static Discharge Voltage       | >2000\          |

| (per MIL-STD-883, Method 3015) |                 |

# **Operating Conditions**

| Parameter          | Description                                 | Min.  | Тур. | Max.  | Unit |

|--------------------|---------------------------------------------|-------|------|-------|------|

| V <sub>DD3.3</sub> | Supply Voltage                              | 3.135 |      | 3.465 | V    |

| V <sub>DD2.5</sub> | Supply Voltage                              | 2.375 |      | 2.625 | V    |

| T <sub>A</sub>     | Operating Temperature (Ambient Temperature) | 0     |      | 70    | °C   |

| C <sub>OUT</sub>   | Output Capacitance                          |       | 6    |       | pF   |

| C <sub>IN</sub>    | Input Capacitance                           |       | 5    |       | pF   |

# **Electrical Characteristics** Over the Operating Range

| Parameter        | Description                                                               | Test Conditions                                    | Min.                         | Тур.               | Max.                         | Unit |

|------------------|---------------------------------------------------------------------------|----------------------------------------------------|------------------------------|--------------------|------------------------------|------|

| V <sub>IL</sub>  | Input LOW Voltage                                                         | For all pins except SMBus                          |                              |                    | 0.8                          | V    |

| V <sub>IH</sub>  | Input HIGH Voltage                                                        |                                                    | 2.0                          |                    |                              | V    |

| I <sub>IL</sub>  | Input LOW Current                                                         | V <sub>IN</sub> = 0V                               |                              |                    | 50                           | μΑ   |

| I <sub>IH</sub>  | Input HIGH Current                                                        | $V_{IN} = V_{DD}$                                  |                              |                    | 50                           | μΑ   |

| I <sub>OH</sub>  | Output HIGH Current                                                       | V <sub>DD</sub> = 2.375V<br>V <sub>OUT</sub> = 1V  |                              |                    |                              |      |

| I <sub>OL</sub>  | Output LOW Current V <sub>DD</sub> = 2.375V 26 35 V <sub>OUT</sub> = 1.2V |                                                    |                              |                    |                              | mA   |

| $V_{OL}$         | Output LOW Voltage <sup>[2]</sup>                                         | $I_{OL} = 12 \text{ mA}, V_{DD} = 2.375 \text{V}$  |                              |                    | 0.6                          | V    |

| V <sub>OH</sub>  | Output HIGH Voltage <sup>[2]</sup>                                        | $I_{OH} = -12 \text{ mA}, V_{DD} = 2.375 \text{V}$ | 1.7                          |                    |                              | V    |

| I <sub>DD</sub>  | Supply Current <sup>[2]</sup><br>(DDR-Only mode)                          | Unloaded outputs, 133 MHz                          |                              |                    | 400                          | mA   |

| I <sub>DD</sub>  | Supply Current (DDR-Only mode)                                            | Loaded outputs, 133 MHz                            |                              |                    | 500                          | mA   |

| I <sub>DDS</sub> | Supply Current                                                            | PWR_DWN# = 0                                       |                              |                    | 100                          | μΑ   |

| V <sub>OUT</sub> | Output Voltage Swing                                                      | See Test Circuity (Refer to Figure 1)              | 0.7                          |                    | V <sub>DD</sub> + 0.6        | V    |

| V <sub>OC</sub>  | Output Crossing Voltage                                                   |                                                    | (V <sub>DD</sub> /2)<br>-0.1 | V <sub>DD</sub> /2 | (V <sub>DD</sub> /2)<br>+0.1 | V    |

| IN <sub>DC</sub> | Input Clock Duty Cycle                                                    |                                                    | 48                           |                    | 52                           | %    |

#### Note

<sup>2.</sup> Parameter is guaranteed by design and characterization. Not 100% tested in production.

# Switching Characteristics<sup>[3]</sup>

| Parameter       | Name                                           | Test Conditions                                                          | Min.                    | Тур. | Max.                    | Unit |

|-----------------|------------------------------------------------|--------------------------------------------------------------------------|-------------------------|------|-------------------------|------|

|                 | Operating Frequency                            |                                                                          | 66                      |      | 180                     | MHz  |

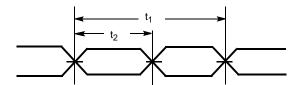

|                 | Duty Cycle <sup>[2,4]</sup> = $t_2 \div t_1$   | Measured at 1.4V for 3.3V outputs<br>Measured at VDD/2 for 2.5V outputs. | IN <sub>DC</sub><br>-5% |      | IN <sub>DC</sub><br>+5% | %    |

| t <sub>3</sub>  | SDRAM Rising Edge Rate <sup>[2]</sup>          | Measured between 0.4V and 2.4V                                           | 1.0                     |      | 2.50                    | V/ns |

| t <sub>4</sub>  | SDRAM Falling Edge Rate <sup>[2]</sup>         | Measured between 2.4V and 0.4V                                           | 1.0                     |      | 2.50                    | V/ns |

| t <sub>3d</sub> | DDR Rising Edge Rate <sup>[2]</sup>            | Measured between 20% to 80% of output (Refer to Figure 1)                | 0.5                     |      | 1.50                    | V/ns |

| t <sub>4d</sub> | DDR Falling Edge Rate <sup>[2]</sup>           | Measured between 20% to 80% of output (Refer to Figure 1)                | 0.5                     |      | 1.50                    | V/ns |

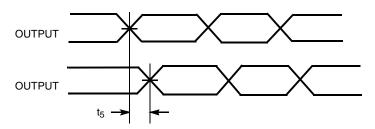

| t <sub>5</sub>  | Output to Output Skew <sup>[2]</sup>           | All outputs equally loaded                                               |                         |      | 100                     | ps   |

| t <sub>6</sub>  | Output to Output Skew for SDRAM <sup>[2]</sup> | All outputs equally loaded                                               |                         |      | 150                     | ps   |

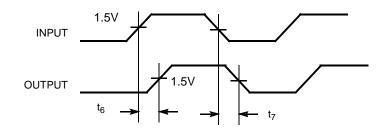

| t <sub>7</sub>  | SDRAM Buffer HH Prop. Delay <sup>[2]</sup>     | Input edge greater than 1 V/ns                                           | 5                       |      | 10                      | ns   |

| t <sub>8</sub>  | SDRAM Buffer LLProp. Delay <sup>[2]</sup>      | Input edge greater than 1 V/ns                                           | 5                       |      | 10                      | ns   |

# **Switching Waveforms**

# **Duty Cycle Timing**

#### All Outputs Rise/Fall Time

OUTPUT

$$0.4V$$

$0.4V$   $0.4V$

### **Output-Output Skew**

#### Note:

- All parameters specified with loaded outputs.

Duty cycle of input clock is 50%. Rising and falling edge rate is greater than 1V/ns.

# Switching Waveforms (continued)

#### **SDRAM Buffer HH and LL Propagation Delay**

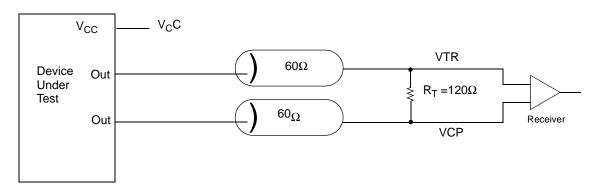

Figure 1 shows the differential clock directly terminated by a 120  $\Omega$  resistor.

Figure 1. Differential Signal Using Direct Termination Resistor

# **Ordering Information**

| Ordering Code | Package Type | Operating<br>Range |

|---------------|--------------|--------------------|

| W256H         | 28-pin SSOP  | Commercial         |

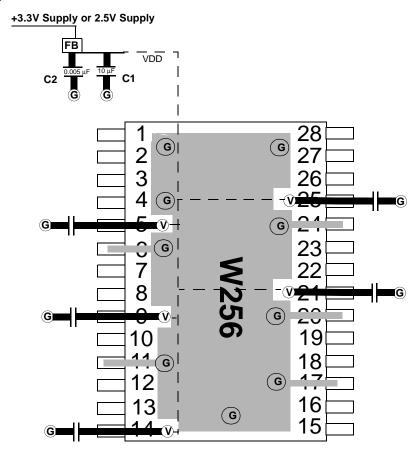

#### Layout Example Single Voltage

FB = Dale ILB1206 - 300 (300 $\Omega$  @ 100 MHz)

Cermaic Caps C1 = 10–22  $\mu F$  C2 = 0.005  $\mu F$

G = VIA to GND plane layer V =VIA to respective supply plane layer

Note: Each supply plane or strip should have a ferrite bead and capacitors All bypass caps = 0.1  $\mu F$  ceramic

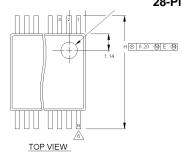

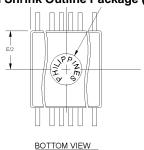

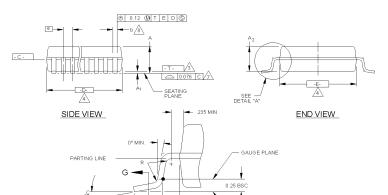

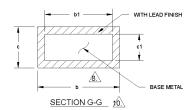

# **Mechanical Package Outline**

#### 28-Pin Small Shrink Outline Package (SSOP, 209 mils)

DETAIL 'A'

- MAXIMUM DIE THICKNESS ALLOWABLE IS 0.43mm (.017 INCHES). DIMENSIONING & TOLERANCES PER ANSI.Y14.5M-1982.

- "T" IS A REFERENCE DATUM.

- \*\* "O" & "E" ARE REFERENCE DATUMS AND DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS, BUT DO INCLUDE MOLD FLASH OR PROTRUSIONS, BUT AT THE PARTING LINE, MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.15mm PER SIDE.

DIMENSION IS THE LENGTH OF TERMINAL FOR SOLDERING TO A SUBSTRATE.

TERMINAL POSITIONS ARE SHOWN FOR REFERENCE ONLY.

- TERMINAL POSITIONS ARE SHOWN FOR REPRENCE UNIT.

FORMED LEADS SHALL BE PLANAR WITH RESPECT TO

ONE ANOTHER WITHIN 0.08mm AT SEATING PLANE.

DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION/INTRUSION.

ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13mm TOTAL IN

EXCESS OF B DIMENSION AT MAXIMUM MATERIAL CONDITION.

DAMBAR INTRUSION SHALL NOT REDUCE DIMENSION B BY MORE

THAN 0.07mm AT LEAST MATERIAL CONDITION.

CONTROLLING DIMENSION: MILLIMETERS.

- THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 AND 0.25mm FROM LEAD TIPS.

- THIS PACKAGE OUTLINE DRAWING COMPLIES WITH JEDEC SPECIFICATION NO. MO-150 FOR THE LEAD COUNTS SHOWN

#### THIS TABLE IN MILLIMETERS

| S      |                | COMMO     | N    |                  | NOTE   |       | 4     |

|--------|----------------|-----------|------|------------------|--------|-------|-------|

| M<br>B | DI             | MENSIO    | NS   | N <sub>OTE</sub> | VARI-  |       | D     |

| °L     | MIN.           | NOM.      | MAX. | Tε               | ATIONS | MIN.  | NO    |

| Α      | 1.73           | 1.86      | 1.99 |                  | AA     | 6.07  | 6.20  |

| Aı     | 0.05           | 0.13      | 0.21 |                  | AB     | 6.07  | 6.20  |

| Αo     | 1.68           | 1.73      | 1.78 |                  | AC     | 7.07  | 7.20  |

| b      | 0.25           | -         | 0.38 | 8,10             | AD     | 8.07  | 8.20  |

| b1     | 0.25           | 0.30      | 0.33 | 10               | AE     | 10.07 | 10.20 |

| С      | 0.09           | -         | 0.20 | 10               | AF     | 10.07 | 10.20 |

| c1     | 0.09           | 0.15      | 0.16 | 10               |        |       |       |

| D      | SEE            | VARIATION | is   | 4                |        |       |       |

| Е      | 5.20           | 5.30      | 5.38 | 4                |        |       |       |

| е      |                | 0.65 BSC  |      |                  |        |       |       |

| Н      | 7.65           | 7.80      | 7.90 |                  |        |       |       |

| L      | 0.63           | 0.75      | 0.95 | 5                |        |       |       |

| L1     | 1.25 REF.      |           |      |                  |        |       | 10    |

| N      | SEE VARIATIONS |           |      | 6                |        |       | 18    |

| 00     | 0°             | 4°        | 8°   |                  |        |       |       |

| R      | 0.09           | 0.15      |      |                  |        |       |       |

VARIATION AF S DESIGNED BUT NOT TOOLED

#### THIS TABLE IN INCHES

|                |           |           | _    |                  |        |      |      |      |    |

|----------------|-----------|-----------|------|------------------|--------|------|------|------|----|

| S              |           | COMMON    |      |                  | NOTE   |      | 4    |      | 6  |

| M<br>B         | DI        | MENSIO    | NS   | N <sub>OTE</sub> | VARI-  |      | D    |      | N  |

| 2              | MIN.      | NOM.      | MAX. | T <sub>E</sub>   | ATIONS | MIN. | NOM. | MAX. |    |

| Α              | .068      | .073      | .078 |                  | AA     | .239 | .244 | .249 | 14 |

| A <sub>1</sub> | .002      | .005      | .008 |                  | AB     | .239 | .244 | .249 | 16 |

| A <sub>2</sub> | .066      | .068      | .070 |                  | AC     | .278 | .284 | .289 | 20 |

| b              | .010      | -         | .015 | 8,10             | AD     | .318 | .323 | .328 | 24 |

| b1             | .010      | .012      | .013 | 10               | AE     | .397 | .402 | .407 | 28 |

| С              | .004      | -         | .008 | 10               | AF     | .397 | .402 | .407 | 30 |

| c1             | .004      | .006      | .006 | 10               |        |      |      |      |    |

| D              | SEE       | VARIATION | NS   | 4                | 1      |      |      |      |    |

| Е              | .205      | .209      | .212 | 4                |        |      |      |      |    |

| е              |           | 0256 BSC  |      |                  |        |      |      |      |    |

| Н              | .301      | .307      | .311 |                  | 1      |      |      |      |    |

| L              | .025      | .030      | .037 | 5                |        |      |      |      |    |

| L1             | .049 REF. |           |      | 1                |        |      |      |      |    |

| Ŋ              | SEE       | VARIATION | 4S   | 6                | 1      |      |      |      |    |

| oc             | 0°        | 4°        | 8°   |                  |        |      |      |      |    |

| R              | 004       | 006       |      |                  | 1      |      |      |      |    |

| Document Title: W256 12 Output Buffer for 2 DDR and 3 SRAM DIMMS Document Number: 38-07256 |        |          |                       |                                               |  |  |  |

|--------------------------------------------------------------------------------------------|--------|----------|-----------------------|-----------------------------------------------|--|--|--|

| REV. ECN NO. Issue Orig. of Change                                                         |        |          | Description of Change |                                               |  |  |  |

| **                                                                                         | 110521 | 12/04/01 | SZV                   | Change from Spec number: 38-01083 to 38-07256 |  |  |  |

| *A                                                                                         | 112153 | 03/01/02 | IKA                   | Added 333 MHz for SDRAM                       |  |  |  |